The Bonder War – An update on ASMPT (522 HK),BESI (BESI NA), Shibaura (6590 JP), Tazmo (6266 JP) and other advanced packaging equipment players

Recently, there were a few advanced semiconductor packaging equipment companies experienced significant stock price drops after announcing their second-quarter earnings report. For example, ASMPT (522 HK) listed in Hong Kong plummeted 34% within two days after its 2Q24 earnings call, and BESI (BESI NA) listed in the Netherlands fell 24% within two days after its 2Q24 earnings call. This has caused considerable concern among investors, and many readers have also asked for an update on the latest situation of advanced packaging equipment companies. Therefore, today, I will provide an update on the latest development of the three major advanced packaging processes, namely HBM, CoWoS, and SoIC.

First, let's review the basic background of CoWoS. We know that TSMC's CoWoS advanced packaging process is a general term, and CoWoS (chip-on-wafer-on-substrate) technology is divided into three types: CoWoS-S, CoWoS-R, and CoWoS-L (see table below):

CoWoS-S is the earliest type, where 'S' stands for silicon. Its interposer is made from a silicon wafer, providing very dense wiring and fast signal transmission. However, its disadvantages are also apparent: 1) high cost (compared to organic interposers), 2) limited by the reticle size of silicon wafer lithography process (the maximum size is 33mm x 26mm = 858mm^2). Although TSMC uses stitching techniques to extend the maximum size of CoWoS-S silicon interposers to 4x reticle limit (e.g., used in AMD MI300), this is the maximum size possible, and it brings another issue: the thin silicon interposer becomes increasingly fragile as its size increases, risking cracking throughout the manufacturing process.

Due to these issues, TSMC developed the second type, CoWoS-R, where 'R' stands for RDL (Re-Distribution Layer). Unlike the silicon interposer, the RDL interposer is made of organic material (usually ABF) and is built up layer by layer through dry film lamination. It is much cheaper than the silicon interposer, though it sacrifices I/O density compared to CoWoS-S.

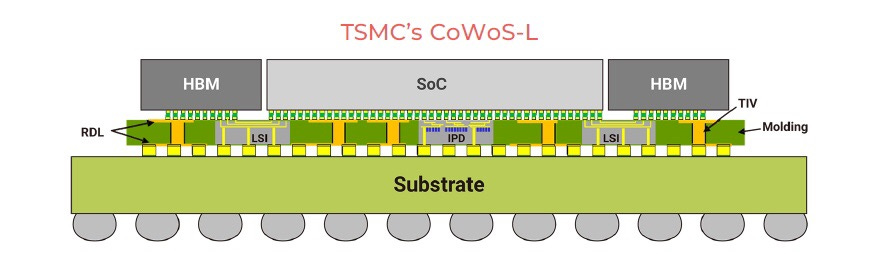

The third type, CoWoS-L, combines the advantages of CoWoS-S and CoWoS-R. CoWoS-L still uses organic RDL interposers (thus cheaper than CoWoS-S) but embeds silicon bridges (both active and passive) in the RDL layers for die-to-die interconnections (see picture below). The passive parts are called IPDs (integrated passive devices), and the active parts are called LSIs (local silicon interconnects). Therefore, it is named CoWoS-L, where L stands for LSI. To put in another way, since using a whole silicon interposer is too expensive, TSMC cuts the whole silicon interposer into sections of silicon bridges, and then embeds them into cheaper organic interposers. By embedding silicon bridges only where chip interconnections are needed, CoWoS-L achieves cost savings, maintains high I/O density, and increases the interposer size (up to 6x reticle limit).

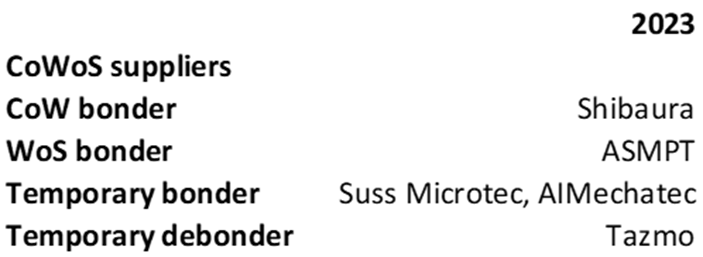

After understanding different types of CoWoS, we also need to know the various bonders used in TSMC's CoWoS process. CoWoS is divided into CoW (chip-on-wafer) and WoS (wafer-on-substrate) processes. The CoW process currently uses Shibaura's FC (flip-chip) bonder, while the WoS process mainly uses ASMPT's bonder. Additionally, the CoWoS process involves temporary bonder & debonder (i.e. TBDB process), which is critical for TSV formation on interposers (please see my previous article on TBDB process: SUSS MicroTec (SMHN GR) -- A Hidden Advanced Packaging Play). TSMC's RDL interposer's temporary bonder is provided by Germany's Suss Microtec, while the silicon interposer's temporary bonder by Japan's AIMechatec, and CoWoS debonder is provided by Japan's Tazmo (see table below):

After introducing the background knowledge, in the following paragraphs I will: 1) update the latest numbers of TSMC's CoWoS-S/L/R production capacity on quarterly and annual basis, 2) explain the latest order situation of advanced packaging equipment manufacturers such as Shibaura, BESI, Protec, Tazmo, EO Technics, ASMPT, K&S, 3) update TSMC's latest CPO and SOIC production capacity plan, 4) explain TSMC's current SOIC customers and each of their SOIC projects in detail.