In my previous article, I introduced two companies related to Google TPU: Celestica & Flex(Celestica (CLS US) vs. Flex (FLEX US) – Who is the Google TPU Winner?). Today, I will introduce two companies related to Amazon ASIC chips: Marvell & Alchip.

First of all, a brief overview of the background: Amazon Web Service (AWS) AI servers use both NVDA's GPGPU and their own ASIC chips. Amazon's ASIC chips are divided into two categories: Tranium chip for training and Inferentia chip for inference. Amazon has an in-house team developing ASIC chips (called Annapurna Labs). However, due to limited in-house resources, Amazon also hires third-party IC design service companies to assist in ASIC chip design. For example, Alchip in Taiwan mainly assists Annapurna in backend chip design, while Marvell in the United States does both frontend and backend chip design together. Currently, Alchip's projects include AWS Tranium 1 and Inferentia 2, while Marvell's projects include AWS Tranium 2 and Inferentia 2.5. Amazon's third-generation ASIC chip project has not been finalized yet.

Let's take a look at the ASIC project by Marvell first. AWS Tranium 2 and Inferentia 2.5 in fact has the same ASIC die. However, Inferentia 2.5 uses a CoWoS packaging of 1 ASIC die + 2 HBM dies, while Tranium 2, due to higher computational requirements for training, uses a CoWoS packaging of 2 ASIC dies + 4 HBM dies.

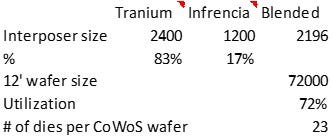

According to my supply chain research, Marvell's ASIC chips will officially enter mass production from 3Q24. Over the two-year project cycle of 2024 and 2025, Marvell has booked a total of TSMC CoWoS capacity for 43k wafers. The majority of shipments will consist of Tranium 2 with a small quantity of Inferentia 2.5. Each Tranium 2 substrate size is approximately 2400 square millimeters, i.e., ~3x reticle size. Thus, one CoWoS wafer can yield ~20 Tranium 2 dies (see table below). Based on Marvell's CoWoS wafer volume seen from TSMC, it can be inferred that the entire project cycle will produce a total of 43k x 23 ~ 1mn ASIC chips, generating approximately $4bn in revenue for Marvell at a unit price of $4k:

Now, let's take a look at Alchip's situation. During the recent earnings call, Alchip stated that the company's mass production revenue (mainly from AWS ASIC chips) will continue to grow in 2Q24 and 3Q24 sequentially, but a QoQ decline is expected in 4Q24. As mentioned earlier, Marvell's AWS ASIC chips will start mass production from 3Q24. Therefore, it can be inferred that 3Q24 should be a transition period for AWS ASIC chips, during which Marvell's Tranium 2 will begin to replace Alchip's Inferentia 2 to ramp up.

In the following paragraphs, I will illustrate detailed quarterly CoWoS wafer volume of Alchip and Marvell at TSMC, and estimate Alchip’s 2025 revenue based on the CoWoS numbers.

Keep reading with a 7-day free trial

Subscribe to Global Technology Research to keep reading this post and get 7 days of free access to the full post archives.